PREVIEW

PREVIEWPart Number

UM3403

Description

3.3V Quad LVCMOS Differential Line Receiver Translator

Status

PREVIEW

Numbers of transmitters

0

Numbers of receivers

4

Protocols

LVDS

Supply Voltage Range (V)

3 to 3.6

Max Data Rate(Mbps)

400

ICC (Max) (mA)

15

ESD HBM (kV)

±8

Operating Temperature Range(℃)

-40 to 85

Package

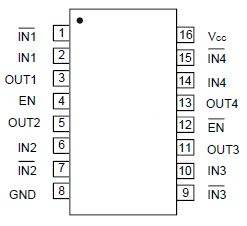

TSSOP16

The UM3403UG is a quad-channel LVDS line receiver/translator offering data rates up to 400 Mbps (200MHz) and low power consumption. The UM3403UG receiver incorporates input fail-safe protection circuit that provides a known output voltage under input open-circuit and terminated (100Ω) conditions. The four independent inputs accept differential signals such as: M-LVDS, LVDS, LVPECL and HCSL and translates them to a single-ended, 3.3 V LVCMOS.

The UM3403UG also offers active high and active low enable/disable inputs (EN and /EN) that allow users to control outputs of all four receivers. These inputs enable or disable the receivers and switch the outputs to an active or high impedance state respectively. The high impedance mode feature helps to reduce the quiescent power consumption to less than 10 mW typical, when the outputs of one or more UM3403UG devices are multiplexed together.

- Accepts M-LVDS, LVDS, LVPECL and HCSL Differential Input Signal Levels

- Maximum Data Rate of 400 Mbps

- Maximum Clock Frequency of 200 MHz

- 25 ps Typical Channel-to-Channel Skew

- 3.3 ns Maximum Propagation Delay

- 3.3 V ±10% Power Supply

- High Impedance Outputs When Disabled

-- Low Quiescent Power < 10 mW Typical

- Supports Open and Terminated Input Fail−safe

- -40°C to +85°C Ambient Operating Temperature

- 16Pin TSSOP

- Pb−Free Device

- Point−to−point Data Transmission

- Backplane Receivers

- Clock Distribution Networks

- Multidrop Buses

| Part Number | Packaging Type | Marking Code | Shipping Qty |

|---|---|---|---|

| UM3403UG | TSSOP16 | UM3403UG | 3000pcs/13Inch Tape & Reel |