# Wide Supply RS-485 Transceiver with 1.65V-5.5V I/O Interface UM13430DA DFN10 3.0×3.0

#### **General Description**

The UM13430DA is a 3.0V to 5.5V RS-485 transceiver designed to meet the increasing system requirements found in today's communication, infrastructure and industrial equipment environments. This is a wide supply (3.0V to 5.5V) device that operates at maximum data rate of 10 Mbps and features a 1.65V to 5.5V I/O logic supply, simplifying multi-voltage system interfacing requirements.

The receiver includes full fail-safe circuitry, guaranteeing a logic-high receiver output when the receiver inputs are open, shorted or floating. The UM13430DA receiver input impedance is at least  $96k\Omega$  (1/8 unit load), allowing more than 256 devices on the bus.

The driver is protected by short circuit detection as well as thermal shutdown and maintains high impedance in shutdown or when powered off. The UM13430DA does not have slew limiting and is intended for high-speed applications requiring data rates up to 10Mbps.

The chip can enter a 1µA low current shutdown mode for extreme power savings.

The UM13430DA is a half-duplex device that operates at max data rates of 10Mbps. It is available in a 10-pin DFN package.

#### **Applications**

- Telecom Infrastructure

- High Speed data links

- Low Voltage μC Communications

- Industrial control equipment

- Building security and automation

#### **Features**

- Wide 3.0V to 5.5V supply operation

- 1.65V to 5.5V I/O logic interface V<sub>L</sub> pin

- Max data rate of 10Mbps

- 1/8 unit load, up to 256 receivers

- Robust ESD protection for RS-485 bus pins

- Driver short circuit limit and thermal shutdown for overload protection

- $-40 \,\mathrm{C}$  to 85  $\mathrm{C}$  operating temperature range

- Lead-free (RoHS 6) DFN

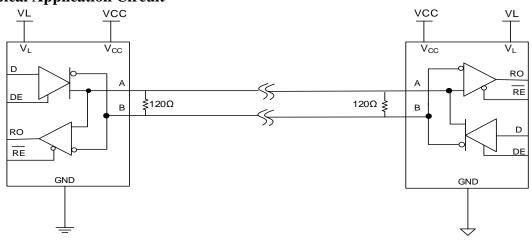

#### **Typical Application Circuit**

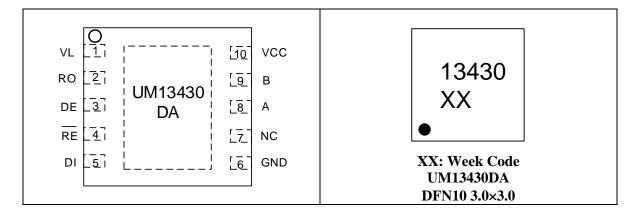

# **Pin Configurations**

# **Top View**

# **Pin Description**

| Pin Number | Symbol      | Description                                                                                       |

|------------|-------------|---------------------------------------------------------------------------------------------------|

| 1          | $V_{\rm L}$ | I/O power supply, sets the logic levels for RO, DE, $\overline{RE}$ and DI                        |

| 2          | RO          | Receiver Output                                                                                   |

| 3          | DE          | Driver enable, driver active when $DE = 1$ ,<br>disabled when $DE = 0$                            |

| 4          | RE          | Receiver enable, receiver is disabled when $\overline{RE} = 1$ , enabled when $\overline{RE} = 0$ |

| 5          | DI          | Driver input                                                                                      |

| 6          | GND         | Ground                                                                                            |

| 7          | NC          | No connection, can be connected to ground                                                         |

| 8          | A           | RS-485 half-duplex non-inverting receiver input and non-inverting driver output                   |

| 9          | В           | RS-485 half-duplex inverting receiver input and inverting driver output                           |

| 10         | $V_{CC}$    | Power supply                                                                                      |

# **Ordering Information**

| Part Number | Packaging Type | Marking Code | <b>Shipping Qty</b>           |

|-------------|----------------|--------------|-------------------------------|

| UM13430DA   | DFN10 3.0×3.0  | 13430        | 3000pcs/13Inch<br>Tape & Reel |

#### **Absolute Maximum Ratings (Note 1)**

| Symbol                  | Parameter                                    | Value                       | Unit           |

|-------------------------|----------------------------------------------|-----------------------------|----------------|

| $V_{CC}$                | V <sub>CC</sub> Supply Voltage               | -0.3 to +6.0                | V              |

| $V_{L}$                 | Logic Interface Voltage                      | -0.3 to +6.0                | V              |

| $V_{DE},V_{DI},V_{/RE}$ | Logic Input Voltage                          | -0.3 to +6.0                | V              |

| $V_{RO}$                | Receiver Output Voltage                      | -0.3 to V <sub>L</sub> +0.3 | V              |

| $V_A/V_B$               | Driver Output Voltage/Receiver Input Voltage | -7.5 to +12.5               | V              |

| Тор                     | Operating Temperature Range                  | -40 to +85                  | $\mathcal C$   |

| $T_J$                   | Operating Junction Temperature               | -40 to +125                 | $\mathcal C$   |

| $T_{STG}$               | Storage Temperature Range                    | -65 to +150                 | $\mathcal{C}$  |

| $T_{\rm L}$             | Lead Temperature (Soldering, 10s)            | +260                        | ${\mathcal C}$ |

Note 1: Maximum ratings are those values beyond which device damage can occur. Maximum ratings applied to the device are individual stress limit values (not normal operating conditions) and are not valid simultaneously. If these limits are exceeded, device functional operation is not implied, damage may occur and reliability may be affected.

#### **Package Thermal Impedance**

| Symbol                 | Parameter                              | Value | Unit |

|------------------------|----------------------------------------|-------|------|

| $\theta_{\mathrm{JA}}$ | Junction-to-ambient thermal resistance | 41    | C/W  |

| $\theta_{ m JC}$       | Junction-to-case thermal resistance    | 9     | °C/W |

#### **ESD Rating**

| Symbol     | Parameter                                        | Value      | Unit |

|------------|--------------------------------------------------|------------|------|

| ESD        | HBM - Human Body Model<br>(RS-485 bus pins A, B) | ±8         | kV   |

| Protection | HBM - Human Body Model (all other pins)          | <u>±</u> 4 | 11 , |

#### **Electrical Characteristics**

(V<sub>CC</sub> = +3V to +5.5V, V<sub>L</sub> = +1.65V to V<sub>CC</sub>,  $T_A$  = -40 °C to +85 °C, unless otherwise noted.)

| Symbol                   | Parameter                                                                 | <b>Test Conditions</b>                      | Min                 | Тур                | Max                    | Unit       |

|--------------------------|---------------------------------------------------------------------------|---------------------------------------------|---------------------|--------------------|------------------------|------------|

| Power Suj                | pply                                                                      |                                             |                     |                    |                        |            |

| $V_{CC}$                 | Supply-Voltage Range                                                      |                                             | 3.0                 |                    | 5.5                    | <b>T</b> 7 |

| $V_{L}$                  | Supply-Voltage Range                                                      |                                             | 1.65                |                    | $V_{CC}$               | V          |

| $I_{CC}$                 | Supply Current                                                            |                                             |                     |                    | 2                      | mA         |

| $I_{SHDN}$               | Supply Current in Shutdown Mode                                           |                                             |                     | 1                  | 10                     | μА         |

| Driver DO                | C Characteristics                                                         |                                             |                     |                    |                        |            |

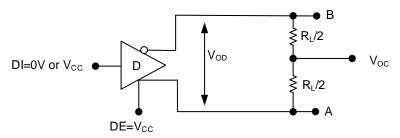

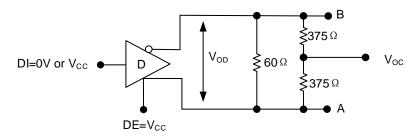

| $V_{\mathrm{OD}}$        | Differential Driver Output                                                | Figure 1 $R_L=54 \Omega, V_{CC}=3.3V$       | 1.5                 |                    | V <sub>CC</sub>        | V          |

|                          |                                                                           | $R_L=54~\Omega,~V_{CC}=4.5V$                | 2                   |                    | $V_{CC}$               | V          |

| $\Delta V_{OD}$ (Note1)  | Change in Magnitude of Differential Output Voltage                        | Figure 1, $R_L=54 \Omega$                   | -0.2                |                    | 0.2                    | V          |

| $V_{OC}$                 | Driver Common Mode<br>Output Voltage (Steady State)                       | Figure 1, $R_L$ =54 $\Omega$                |                     | V <sub>CC</sub> /2 | 3                      | V          |

| $\Delta V_{OC}$ (Note1)  | Change in Driver Common<br>Mode Output Voltage                            | Figure 1, $R_L=54 \Omega$                   | -0.2                |                    | 0.2                    | V          |

| I <sub>A, B</sub>        | Input Current (A or B)                                                    | $V_{OUT}$ =12V, DE=0V, $V_{CC}$ =0V or 5.5V |                     |                    | 125                    | μА         |

| -                        | input Current (A or B)                                                    | $V_{OUT}$ =-7V, DE=0V, $V_{CC}$ =0V or 5.5V | -100                |                    |                        | μА         |

| I <sub>OSD</sub> (Note2) | Driver short circuit output current                                       | $-7V \le V_{OUT} \le 12V$                   | -250                |                    | 250                    | mA         |

| Receiver I               | DC Characteristics                                                        |                                             |                     |                    |                        |            |

| $V_{\text{TH}}$          | Receiver Differential Threshold Voltage (V <sub>A</sub> -V <sub>B</sub> ) | -7V≤V <sub>CM</sub> ≤ 12V                   | -200                |                    | -50                    | mV         |

| $\Delta V_{TH}$          | Receiver Input Hysteresis                                                 | $V_{CM}=0V$                                 |                     | 25                 |                        | mV         |

| $R_{\rm IN}$             | Receiver Input Resistance                                                 | -7V≤V <sub>CM</sub> ≤ 12V                   | 96                  |                    |                        | kΩ         |

| $I_{OSR}$                | Receiver Output Short Circuit Current                                     | $0V\!\!\leq\!\!V_{RO}\!\!\leq V_L$          | -100                |                    | 100                    | mA         |

| $I_{OZR}$                | High-Z receiver output current                                            | $0V \leq V_{OUT} \leq VL$                   | -1                  |                    | 1                      | μΑ         |

| Logic Inp                | out and Output                                                            |                                             |                     |                    |                        |            |

| $ m V_{IH}$              | Logic Input thresholds (DI,                                               | Logic Input High                            | $2/3 *V_L$          |                    |                        | V          |

| $V_{\text{IL}}$          | DE, $\overline{RE}$ )<br>1.65 $V \le V_L \le 5.5V \& V_L \le V_{CC}$      | Logic Input Low                             |                     |                    | 1/3<br>*V <sub>L</sub> | V          |

| $V_{\mathrm{HYS}}$       | Input Hysteresis (DI, DE, RE)                                             |                                             |                     | 300                |                        | mV         |

| $I_{\rm IN1}$            | Logic Input Current                                                       | DE, DI, RE                                  | -1                  |                    | 1                      | μA         |

| $V_{\mathrm{OH}}$        | Receiver Output High<br>Voltage (RO)                                      | I <sub>OUT</sub> =-1mA                      | V <sub>L</sub> -0.6 |                    |                        | V          |

| V <sub>OL</sub>          | Receiver Output Low Voltage (RO)                                          | I <sub>OUT</sub> =1mA                       |                     |                    | 0.4                    | V          |

Note 1:  $\Delta V_{OD}$  and  $\Delta V_{OC}$  are the changes in  $V_{OD}$  and  $V_{OC}$ , respectively, when the DI input changes state.

Note2: The short-circuit output current is the peak current just prior to current limiting; the short-circuit foldback output current applies during current limiting to allow a recovery from bus contention.

Switching Characteristics ( $V_{CC}$  = +3V to +5.5V,  $V_L$  = +1.65V to + $V_{CC}$ ,  $T_A$  = -40 °C to +85 °C, unless otherwise noted.)

| Symbol                                                                                                   | Parameter                                                                                                                                                                                                                                                                                                                                                                                         | Test Conditions                                                                                                                                                                                                                                                                                                                                     | Min   | Тур  | Max                                         | Unit                    |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|---------------------------------------------|-------------------------|

|                                                                                                          | Characteristics                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                     |       |      |                                             |                         |

| ,                                                                                                        | D: 11 (1 (1:1)                                                                                                                                                                                                                                                                                                                                                                                    | See Figure3                                                                                                                                                                                                                                                                                                                                         |       |      | <b>CO</b>                                   |                         |

| $t_{\mathrm{DPLH}}$                                                                                      | Driver prop delay (low to high)                                                                                                                                                                                                                                                                                                                                                                   | $R_L=54 \Omega, C_L=50 pF$                                                                                                                                                                                                                                                                                                                          |       |      | 60                                          | ns                      |

| 4                                                                                                        | Duiven man delev (high to leve)                                                                                                                                                                                                                                                                                                                                                                   | See Figure3                                                                                                                                                                                                                                                                                                                                         |       |      | 60                                          |                         |

| $t_{DPHL}$                                                                                               | Driver prop delay (high to low)                                                                                                                                                                                                                                                                                                                                                                   | $R_L=54 \Omega, C_L=50pF$                                                                                                                                                                                                                                                                                                                           |       |      | 60                                          | ns                      |

| 4                                                                                                        | Differential Driver Output Skew                                                                                                                                                                                                                                                                                                                                                                   | See Figure3                                                                                                                                                                                                                                                                                                                                         |       |      | 10                                          |                         |

| t <sub>DSKEW</sub>                                                                                       | t <sub>DPLH</sub> - t <sub>DPHL</sub>                                                                                                                                                                                                                                                                                                                                                             | $R_L=54 \Omega, C_L=50 pF$                                                                                                                                                                                                                                                                                                                          |       |      | 10                                          | ns                      |

| + +                                                                                                      | Differential Driver Output Rise                                                                                                                                                                                                                                                                                                                                                                   | See Figure3                                                                                                                                                                                                                                                                                                                                         |       |      | 15                                          | na                      |

| $t_{\rm DR},t_{\rm DF}$                                                                                  | Time or Fall Time                                                                                                                                                                                                                                                                                                                                                                                 | $R_L=54 \Omega, C_L=50 pF$                                                                                                                                                                                                                                                                                                                          |       |      | 13                                          | ns                      |

| £                                                                                                        | Maximum Data Rate                                                                                                                                                                                                                                                                                                                                                                                 | Duty Cycle 40% to                                                                                                                                                                                                                                                                                                                                   |       | 10   |                                             | Mhng                    |

| $f_{MAX}$                                                                                                | Maximum Data Kate                                                                                                                                                                                                                                                                                                                                                                                 | 60%                                                                                                                                                                                                                                                                                                                                                 |       | 10   |                                             | Mbps                    |

| toarr                                                                                                    | Driver Enable to Output High                                                                                                                                                                                                                                                                                                                                                                      | See Figure4                                                                                                                                                                                                                                                                                                                                         |       |      | 100                                         | ne                      |

| t <sub>DZH</sub>                                                                                         | Driver Enable to Output High                                                                                                                                                                                                                                                                                                                                                                      | $R_L=500 \Omega, C_L=50 pF$                                                                                                                                                                                                                                                                                                                         |       |      | 100                                         | ns                      |

| <b>t</b>                                                                                                 | Duivon Enghla to Output I avv                                                                                                                                                                                                                                                                                                                                                                     | See Figure4                                                                                                                                                                                                                                                                                                                                         |       |      | 100                                         | ne                      |

| $t_{\mathrm{DZL}}$                                                                                       | Driver Enable to Output Low                                                                                                                                                                                                                                                                                                                                                                       | $R_L=500 \Omega, C_L=50pF$                                                                                                                                                                                                                                                                                                                          |       |      | 100                                         | ns                      |

| t                                                                                                        | Driver Disable from Output                                                                                                                                                                                                                                                                                                                                                                        | See Figure4                                                                                                                                                                                                                                                                                                                                         |       |      | 100                                         | 10.0                    |

| $t_{ m DHZ}$                                                                                             | High                                                                                                                                                                                                                                                                                                                                                                                              | $R_L=500 \Omega, C_L=50pF$                                                                                                                                                                                                                                                                                                                          |       |      | 100                                         | ns                      |

| 4                                                                                                        | Driver Disable from Output                                                                                                                                                                                                                                                                                                                                                                        | See Figure4                                                                                                                                                                                                                                                                                                                                         |       |      | 100                                         | na                      |

| $t_{DLZ}$                                                                                                | Low                                                                                                                                                                                                                                                                                                                                                                                               | $R_L=500 \Omega, C_L=50pF$                                                                                                                                                                                                                                                                                                                          |       |      | 100                                         | ns                      |

| 4                                                                                                        | Driver Enable from Shutdown                                                                                                                                                                                                                                                                                                                                                                       | See Figure4                                                                                                                                                                                                                                                                                                                                         |       |      | 5000                                        |                         |

| t <sub>DZH(SHDN)</sub>                                                                                   | to output high                                                                                                                                                                                                                                                                                                                                                                                    | $R_L=500 \Omega, C_L=50 pF$                                                                                                                                                                                                                                                                                                                         |       |      | 5000                                        | ns                      |

| _                                                                                                        | Driver Enable from Shutdown                                                                                                                                                                                                                                                                                                                                                                       | See Figure4                                                                                                                                                                                                                                                                                                                                         |       |      | 5000                                        |                         |

| t <sub>DZL(SHDN)</sub>                                                                                   | to output low                                                                                                                                                                                                                                                                                                                                                                                     | $R_L=500 \Omega, C_L=50 pF$                                                                                                                                                                                                                                                                                                                         |       |      | 5000                                        | ns                      |

| $t_{ m SHDN}$                                                                                            | Time to Shutdown                                                                                                                                                                                                                                                                                                                                                                                  | -                                                                                                                                                                                                                                                                                                                                                   |       |      | 1000                                        | ns                      |

| Receiver A                                                                                               | C Characteristics                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                     |       |      |                                             |                         |

| Symbol                                                                                                   | Parameter                                                                                                                                                                                                                                                                                                                                                                                         | Test Conditions                                                                                                                                                                                                                                                                                                                                     | Min   | Тур  | Mari                                        | Unit                    |

|                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                     | 17111 | - JP | Max                                         | Cint                    |

| t                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                   | See Figure5                                                                                                                                                                                                                                                                                                                                         |       |      |                                             |                         |

| $t_{RPLH}$                                                                                               | Receiver prop delay (low to high)                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                     | 30    | 60   | 90                                          | ns                      |

|                                                                                                          | Receiver prop delay (low to high)                                                                                                                                                                                                                                                                                                                                                                 | See Figure5                                                                                                                                                                                                                                                                                                                                         | 30    | 60   | 90                                          | ns                      |

| t <sub>RPLH</sub>                                                                                        | Receiver prop delay (low to high) Receiver prop delay (high to low)                                                                                                                                                                                                                                                                                                                               | See Figure5<br>C <sub>L</sub> =15pF                                                                                                                                                                                                                                                                                                                 |       |      |                                             |                         |

| t <sub>RPHL</sub>                                                                                        | Receiver prop delay (low to high)                                                                                                                                                                                                                                                                                                                                                                 | See Figure5<br>C <sub>L</sub> =15pF<br>See Figure5<br>C <sub>L</sub> =15pF                                                                                                                                                                                                                                                                          | 30    | 60   | 90<br>90                                    | ns<br>ns                |

|                                                                                                          | Receiver prop delay (low to high) Receiver prop delay (high to low)                                                                                                                                                                                                                                                                                                                               | See Figure5<br>C <sub>L</sub> =15pF<br>See Figure5                                                                                                                                                                                                                                                                                                  | 30    | 60   | 90                                          | ns                      |

| t <sub>RPHL</sub>                                                                                        | Receiver prop delay (low to high)  Receiver prop delay (high to low)  Differential Receiver Output  Skew  t_RPLH-t_RPHL                                                                                                                                                                                                                                                                           | See Figure5<br>C <sub>L</sub> =15pF<br>See Figure5<br>C <sub>L</sub> =15pF                                                                                                                                                                                                                                                                          | 30    | 60   | 90<br>90                                    | ns<br>ns                |

| t <sub>RPHL</sub>                                                                                        | Receiver prop delay (low to high)  Receiver prop delay (high to low)  Differential Receiver Output                                                                                                                                                                                                                                                                                                | See Figure5 $C_L=15pF$ See Figure5 $C_L=15pF$ $C_L=15pF$                                                                                                                                                                                                                                                                                            | 30    | 60   | 90<br>90                                    | ns<br>ns                |

| t <sub>RPHL</sub> t <sub>RSKEW</sub>                                                                     | Receiver prop delay (low to high)  Receiver prop delay (high to low)  Differential Receiver Output Skew  trplh-trphl   Maximum Data Rate                                                                                                                                                                                                                                                          | See Figure5 $C_L=15pF$ See Figure5 $C_L=15pF$ $C_L=15pF$ Duty Cycle 40% to                                                                                                                                                                                                                                                                          | 30    | 60   | 90<br>90<br>10                              | ns ns ns Mbps           |

| t <sub>RPHL</sub>                                                                                        | Receiver prop delay (low to high)  Receiver prop delay (high to low)  Differential Receiver Output  Skew  t_RPLH-t_RPHL                                                                                                                                                                                                                                                                           | See Figure5 $C_L=15pF$ See Figure5 $C_L=15pF$ $C_L=15pF$ Duty Cycle 40% to 60%                                                                                                                                                                                                                                                                      | 30    | 60   | 90<br>90                                    | ns<br>ns                |

| t <sub>RPHL</sub> t <sub>RSKEW</sub> f <sub>MAX</sub> t <sub>RZH</sub>                                   | Receiver prop delay (low to high)  Receiver prop delay (high to low)  Differential Receiver Output Skew  t_RPLH-t_RPHL   Maximum Data Rate  Receiver enable to output high                                                                                                                                                                                                                        | See Figure5 $C_L$ =15pF  See Figure5 $C_L$ =15pF $C_L$ =15pF  Duty Cycle 40% to 60%  See Figure6 $R_L$ =1k $\Omega$ , $C_L$ =15pF  See Figure6                                                                                                                                                                                                      | 30    | 60   | 90<br>90<br>10                              | ns ns ns ns ns          |

| t <sub>RPHL</sub> t <sub>RSKEW</sub>                                                                     | Receiver prop delay (low to high)  Receiver prop delay (high to low)  Differential Receiver Output Skew  trplh-trphl   Maximum Data Rate                                                                                                                                                                                                                                                          | See Figure5 $C_L$ =15pF  See Figure5 $C_L$ =15pF $C_L$ =15pF  Duty Cycle 40% to 60%  See Figure6 $R_L$ =1k $\Omega$ , $C_L$ =15pF  See Figure6 $R_L$ =1k $\Omega$ , $C_L$ =15pF                                                                                                                                                                     | 30    | 60   | 90<br>90<br>10                              | ns ns ns Mbps           |

| t <sub>RPHL</sub> t <sub>RSKEW</sub> f <sub>MAX</sub> t <sub>RZH</sub>                                   | Receiver prop delay (low to high)  Receiver prop delay (high to low)  Differential Receiver Output Skew  t_RPLH-t_RPHL   Maximum Data Rate  Receiver enable to output high  Receiver enable to output low                                                                                                                                                                                         | See Figure5 $C_L$ =15pF  See Figure5 $C_L$ =15pF $C_L$ =15pF  Duty Cycle 40% to 60%  See Figure6 $R_L$ =1k $\Omega$ , $C_L$ =15pF  See Figure6 $R_L$ =1k $\Omega$ , $C_L$ =15pF                                                                                                                                                                     | 30    | 60   | 90<br>90<br>10<br>100<br>100                | ns ns ns ns ns ms ns ms |

| t <sub>RPHL</sub> t <sub>RSKEW</sub> f <sub>MAX</sub> t <sub>RZH</sub>                                   | Receiver prop delay (low to high)  Receiver prop delay (high to low)  Differential Receiver Output Skew  t_RPLH-t_RPHL   Maximum Data Rate  Receiver enable to output high                                                                                                                                                                                                                        | See Figure5 $C_L$ =15pF See Figure5 $C_L$ =15pF $C_L$ =15pF  Duty Cycle 40% to 60% See Figure6 $R_L$ =1k $\Omega$ , $C_L$ =15pF See Figure6 $R_L$ =1k $\Omega$ , $C_L$ =15pF See Figure6 $R_L$ =1k $\Omega$ , $C_L$ =15pF                                                                                                                           | 30    | 60   | 90<br>90<br>10                              | ns ns ns ns ns          |

| t <sub>RPHL</sub> t <sub>RSKEW</sub> f <sub>MAX</sub> t <sub>RZH</sub> t <sub>RZL</sub>                  | Receiver prop delay (low to high)  Receiver prop delay (high to low)  Differential Receiver Output Skew  t_RPLH-t_RPHL   Maximum Data Rate  Receiver enable to output high  Receiver enable to output low                                                                                                                                                                                         | See Figure5 $C_L$ =15pF  See Figure5 $C_L$ =15pF $C_L$ =15pF  Duty Cycle 40% to 60%  See Figure6 $R_L$ =1k $\Omega$ , $C_L$ =15pF  See Figure6 $R_L$ =1k $\Omega$ , $C_L$ =15pF  See Figure6                                                                                                                                                        | 30    | 60   | 90<br>90<br>10<br>100<br>100                | ns ns ns Mbps ns ns     |

| t <sub>RPHL</sub> t <sub>RSKEW</sub> f <sub>MAX</sub> t <sub>RZH</sub>                                   | Receiver prop delay (low to high)  Receiver prop delay (high to low)  Differential Receiver Output Skew  trplh-trphl   Maximum Data Rate  Receiver enable to output high  Receiver enable to output low  Receiver Disable from output high  Receiver Disable from output                                                                                                                          | See Figure5 $C_L$ =15pF See Figure5 $C_L$ =15pF $C_L$ =15pF  Duty Cycle 40% to 60% See Figure6 $R_L$ =1k $\Omega$ , $C_L$ =15pF See Figure6 $R_L$ =1k $\Omega$ , $C_L$ =15pF See Figure6 $R_L$ =1k $\Omega$ , $C_L$ =15pF                                                                                                                           | 30    | 60   | 90<br>90<br>10<br>100<br>100                | ns ns ns ns ns ms ns ms |

| t <sub>RPHL</sub> t <sub>RSKEW</sub> f <sub>MAX</sub> t <sub>RZH</sub> t <sub>RZL</sub> t <sub>RHZ</sub> | Receiver prop delay (low to high)  Receiver prop delay (high to low)  Differential Receiver Output Skew  t_RPLH-t_RPHL   Maximum Data Rate  Receiver enable to output high  Receiver enable to output low  Receiver Disable from output high  Receiver Disable from output                                                                                                                        | See Figure5 $C_L$ =15pF  See Figure5 $C_L$ =15pF $C_L$ =15pF  Duty Cycle 40% to 60%  See Figure6 $R_L$ =1k $\Omega$ , $C_L$ =15pF  See Figure6  See Figure6 | 30    | 60   | 90<br>90<br>10<br>100<br>100<br>100         | ns ns ns Mbps ns ns ns  |

| trphl trskew fmax trzh trzl trhz                                                                         | Receiver prop delay (low to high)  Receiver prop delay (high to low)  Differential Receiver Output Skew  trplh-trphl   Maximum Data Rate  Receiver enable to output high  Receiver enable to output low  Receiver Disable from output high  Receiver Disable from output                                                                                                                          | See Figure5 $C_L$ =15pF  See Figure5 $C_L$ =15pF $C_L$ =15pF  Duty Cycle 40% to 60%  See Figure6 $R_L$ =1k $\Omega$ , $C_L$ =15pF                                                                         | 30    | 60   | 90<br>90<br>10<br>100<br>100                | ns ns ns Mbps ns ns     |

| trphl trskew fmax trzh trzl trhz trhz trhz                                                               | Receiver prop delay (low to high)  Receiver prop delay (high to low)  Differential Receiver Output Skew  t_RPLH-t_RPHL   Maximum Data Rate  Receiver enable to output high  Receiver enable to output low  Receiver Disable from output high  Receiver Disable from output low  Receiver enable from shutdown                                                                                     | See Figure5 $C_L$ =15pF  See Figure5 $C_L$ =15pF $C_L$ =15pF  Duty Cycle 40% to 60%  See Figure6 $R_L$ =1k $\Omega$ , $C_L$ =15pF  See Figure6  See Figure6 | 30    | 60   | 90<br>90<br>10<br>100<br>100<br>100<br>5000 | ns ns ns Mbps ns ns ns  |

| t <sub>RPHL</sub> t <sub>RSKEW</sub> f <sub>MAX</sub> t <sub>RZH</sub> t <sub>RZL</sub> t <sub>RHZ</sub> | Receiver prop delay (low to high)  Receiver prop delay (high to low)  Differential Receiver Output Skew  t_RPLH-t_RPHL   Maximum Data Rate  Receiver enable to output high  Receiver enable to output low  Receiver Disable from output high  Receiver Disable from output low  Receiver Disable from output low  Receiver Disable from output low  Receiver Disable from shutdown to output high | See Figure5 $C_L$ =15pF  See Figure5 $C_L$ =15pF $C_L$ =15pF  Duty Cycle 40% to 60%  See Figure6 $R_L$ =1k $\Omega$ , $C_L$ =15pF  See Figure7              | 30    | 60   | 90<br>90<br>10<br>100<br>100<br>100         | ns ns ns Mbps ns ns ns  |

#### **Parameter Measurement Information**

Figure 1. Differential Driver Output Voltage

Figure 2. Differential Driver Output Voltage Over Common Mode

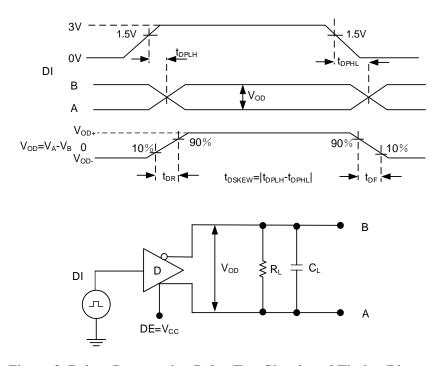

Figure 3. Driver Propagation Delay Test Circuit and Timing Diagram

#### **Parameter Measurement Information (continued)**

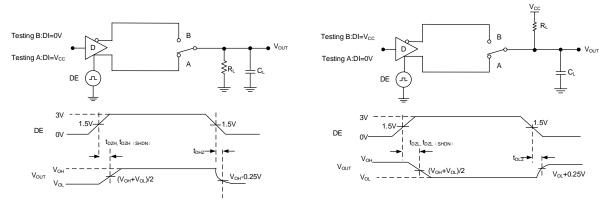

Figure 4. Driver Enable and Disable Timing Test Circuits and Timing Diagrams

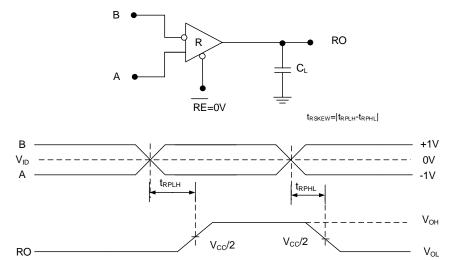

Figure 5. Receiver Propagation Delay Test Circuit and Timing Diagram

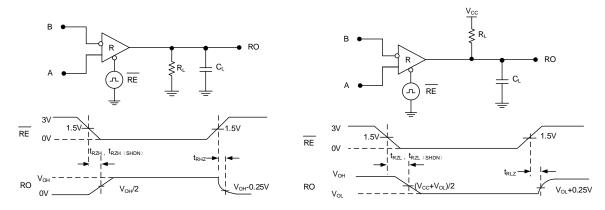

Figure 6. Receiver Enable and Disable Test Circuits and Timing Diagrams

#### **Device Function Table**

| Transmitting    |      |    |        |      |  |

|-----------------|------|----|--------|------|--|

|                 | puts |    |        |      |  |

| $\overline{RE}$ | DE   | DI | A      | В    |  |

| X               | 1    | 1  | 1      | 0    |  |

| X               | 1    | 0  | 0      | 1    |  |

| 0               | 0    | X  | High-Z |      |  |

| 1               | 0    | X  | Shute  | down |  |

| Receiving       |        |                                                                |           |  |

|-----------------|--------|----------------------------------------------------------------|-----------|--|

| _               | Output |                                                                |           |  |

| $\overline{RE}$ | DE     | $ m V_A$ - $ m V_B$                                            | RO        |  |

| 0               | X      | ≥-50mV                                                         | 1         |  |

| 0               | X      | $-200 \text{mV} < V_{\text{A}} - V_{\text{B}} < -50 \text{mV}$ | Undefined |  |

| 0               | X      | ≤-200mV                                                        | 0         |  |

| 0               | X      | Open/Shorted/Idle                                              | 1         |  |

| 1               | 1      | X                                                              | High -Z   |  |

| 1               | 0      | X                                                              | Shutdown  |  |

# **Typical Operating Characteristics**

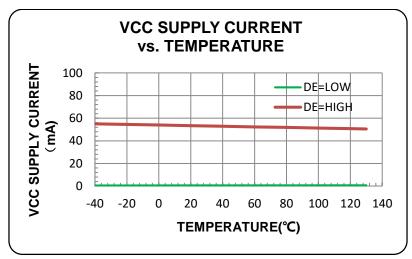

Figure 7. V<sub>CC</sub> Supply Current vs. Temperature

#### **Typical Operating Characteristics (continued)**

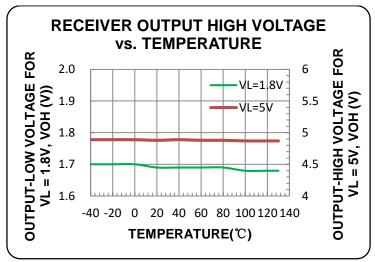

Figure 8. Receiver Output High Voltage vs. Temperature

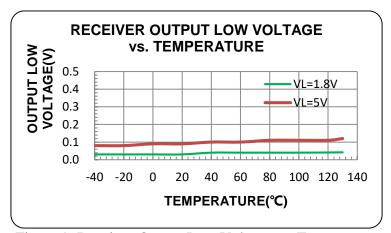

Figure 9. Receiver Output Low Voltage vs. Temperature

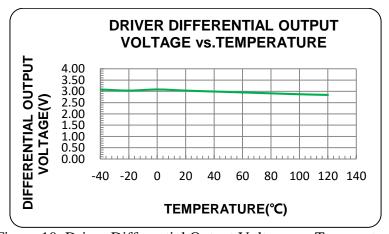

Figure 10. Driver Differential Output Voltage vs. Temperature

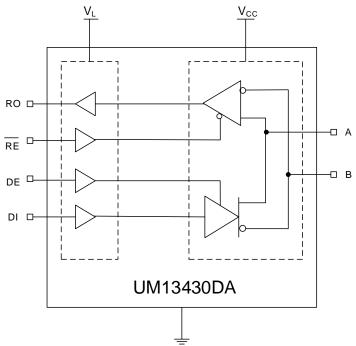

#### **Block Diagram**

Figure 11. Block Diagram:

# **Detail Description**

The UM13430DA high-speed transceivers for RS-485 communication contain one driver and one receiver. These devices feature fail-safe circuitry, which guarantees a logic-high receiver output when the receiver inputs are open or shorted, or when they are connected to a terminated transmission line with all drivers disabled. The UM13430DA driver slew rates are not limited, making transmit speeds up to 10Mbps possible.

The UM13430DA RS-485 transceivers operate with a  $V_{\rm CC}$  voltage supply from 3V to 5.5V Drivers are output short-circuit current limited. Thermal shutdown circuitry protects drivers against excessive power dissipation. When activated, the thermal shutdown circuitry places the driver outputs into a high impedance state.

#### Fail-Safe

The UM13430DA guarantees a logic-high receiver output when the receiver inputs are shorted or open, or when they are connected to a terminated transmission line with all drivers disabled. This is done by setting the receiver threshold between -50mV and -200mV. If the differential receiver input voltage (A-B) is greater than or equal to -50mV, RO is logic high. If A-B is less than or equal to -200mV, RO is logic low. In the case of a terminated bus with all transmitters disabled, the receiver's differential input voltage is pulled to 0V by the termination. With the receiver thresholds of the UM13430DA, this results in a logic high with a 50mV minimum noise margin. Unlike previous fail-safe devices, the -50mV to -200mV threshold complies with the ±200mV EIA/TIA-485 standard.

### **Applications Information**

#### 256 Transceivers on the Bus

The standard RS-485 receiver input impedance is  $12k\Omega$  (one unit load), and the standard driver can drive up to 32 unit loads. The Union family of transceivers have a 1/8 unit load receiver input impedance ( $96k\Omega$ ), allowing up to 256 transceivers to be connected in parallel on one communication line. Any combination of these devices and/or other RS-485 transceivers with a total of 32 unit loads or less can be connected to the line.

#### **Driver Output Protection**

Two mechanisms prevent excessive output current and power dissipation caused by faults or by bus contention. The first, a foldback current limit on the output stage, provides immediate protection against short circuits over the whole common-mode voltage range. The second, a thermal shutdown circuit, forces the driver outputs into a high-impedance state if the die temperature becomes excessive.

#### **Typical Applications**

The UM13430DA transceivers are designed for bidirectional data communications on multipoint bus transmission lines. To minimize reflections, the line should be terminated at both ends in its characteristic impedance, and stub lengths off the main line should be kept as short as possible.

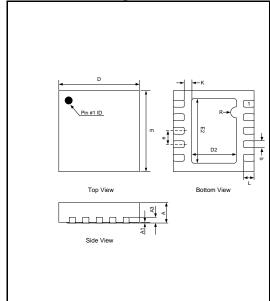

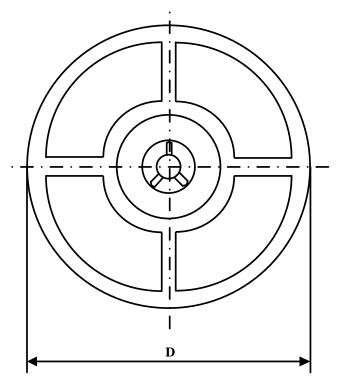

# **Package Information**

# **UM13430DA DFN10 3.0 ×3.0**

# **Outline Drawing**

| DIMENSIONS |             |         |       |        |         |       |

|------------|-------------|---------|-------|--------|---------|-------|

| Crombal    | MILLIMETERS |         |       | INCHES |         |       |

| Symbol     | Min         | Тур     | Max   | Min    | Тур     | Max   |

| A          | 0.70        | 0.75    | 0.80  | 0.028  | 0.030   | 0.032 |

| A1         | 0.00        | 0.02    | 0.05  | 0.000  | 0.001   | 0.002 |

| A3         | (           | 0.20REF |       | (      | 0.008RE | F     |

| b          | 0.20        | 0.25    | 0.30  | 0.008  | 0.010   | 0.012 |

| D          | 2.90        | 3.00    | 3.10  | 0.116  | 0.120   | 0.124 |

| Е          | 2.90        | 3.00    | 3.10  | 0.116  | 0.120   | 0.124 |

| D2         | 1.55        | 1.65    | 1.75  | 0.062  | 0.066   | 0.070 |

| E2         | 2.30        | 2.40    | 2.50  | 0.092  | 0.096   | 0.100 |

| e          | 0.40        | 0.50    | 0.60  | 0.016  | 0.020   | 0.024 |

| K          | 0.175       | 0.275   | 0.375 | 0.007  | 0.011   | 0.015 |

| L          | 0.35        | 0.40    | 0.45  | 0.014  | 0.016   | 0.018 |

| R          |             | 0.20REF |       | (      | 0.008RE | F     |

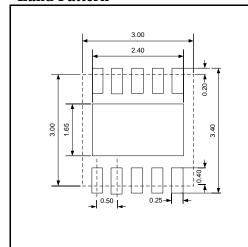

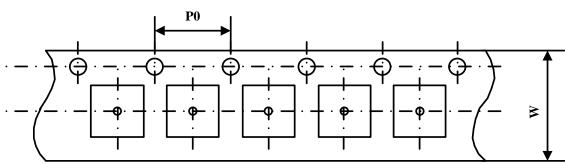

#### **Land Pattern**

#### NOTES:

- 1. Compound dimension:  $3.00 \times 3.00$ ;

- 2. Unit: mm;

- 3. General tolerance ±0.05mm unless otherwise specified;

- 4. The layout is just for reference.

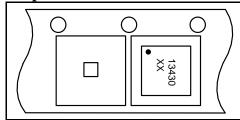

#### **Tape and Reel Orientation**

# **Packing Information**

| Part Number | Package Type  | Carrier Width(W) | Pitch(P0) | Reel Size(D) |

|-------------|---------------|------------------|-----------|--------------|

| UM13430DA   | DFN10 3.0×3.0 | 12 mm            | 4 mm      | 330 mm       |

#### **GREEN COMPLIANCE**

Union Semiconductor is committed to environmental excellence in all aspects of its operations including meeting or exceeding regulatory requirements with respect to the use of hazardous substances. Numerous successful programs have been implemented to reduce the use of hazardous substances and/or emissions.

All Union components are compliant with the RoHS directive, which helps to support customers in their compliance with environmental directives. For more green compliance information, please visit:

http://www.union-ic.com/index.aspx?cat\_code=RoHSDeclaration

#### IMPORTANT NOTICE

The information in this document has been carefully reviewed and is believed to be accurate. Nonetheless, this document is subject to change without notice. Union assumes no responsibility for any inaccuracies that may be contained in this document, and makes no commitment to update or to keep current the contained information, or to notify a person or organization of any update. Union reserves the right to make changes, at any time, in order to improve reliability, function or design and to attempt to supply the best product possible.